### 【19】中華民國 【12】專利公報 (U)

【11】證書號數:M420838

【45】公告日: 中華民國 101 (2012) 年 01 月 11 日 【51】Int. Cl.: *H01L27/10 (2006.01)*

新型 全6頁

【54】名 稱:單埠SRAM

SINGLE PORT SRAM

【21】申請案號:100207250 【22】申請日:中華民國100(2011)年04月25日

【72】創作人: 蕭明椿 (TW) SHIAU, MING CHUEN;廖家正 (TW) LIAO, CHIA CHENG;

莊易蒼 (TW) CHUANG, YI TSANG; 張恩誌 (TW) CHANG, EN CHIH

【71】申 請 人: 修平技術學院 HSIUPING INSTITUTE OF

**TECHNOLOGY**

臺中市大里區工業路 11 號

### [57]申請專利範圍

1. 一種單埠 SRAM,包括:一記憶體陣列,該記憶體陣列係由複數列記憶體晶胞與複數行 記憶體晶胞所組成,每一列記憶體晶胞與每一行記憶體晶胞均包含有複數個記憶體晶胞 (1);以及複數個控制電路(2),每一列記憶體晶胞設置一個控制電路(2);其中,每一記憶 體晶胞(1)更包含:一第一反相器,係由一第一 PMOS 電晶體(P1)與一第一 NMOS 電晶體 (M1)串聯所組成,該第一反相器係連接在一電源供應電壓(VDD)與一第一低電壓節點 (VL1)之間;一第二反相器,係由一第二PMOS電晶體(P2)與一第二NMOS電晶體(M2) 串聯所組成,該第二反相器係連接在該電源供應電壓(VDD)與一第二低電壓節點(VL2)之 間;一儲存節點(A),係由該第一反相器之輸出端所形成;一反相儲存節點(B),係由該 第二反相器之輸出端所形成;一第三 NMOS 電晶體(M3),係連接在該儲存節點(A)與對 應之一位元線(BL)之間,且閘極連接至對應之一字元線(WL);一第三反相器,係由一第 一 PMOS 控制電晶體(PC1)與一第一 NMOS 控制電晶體(MC1)串聯所組成,該第三反相 器係連接在一次電源供應電壓(VDDL)與接地電壓之間,該第三反相器之輸入端連接至該 第一反相器之輸出端(儲存節點 A);一第四反相器,係由一第二 PMOS 控制電晶體(PC2) 與一第二 NMOS 控制電晶體(MC2)串聯所組成,該第四反相器係連接在該次電源供應電 壓(VDDL)與接地電壓之間,該第四反相器之輸入端連至該第二反相器之輸出端(反相儲 存節點 B);一第一控制節點(B1),係由該第四反相器之輸出端所形成,且連接至該第二 NMOS 電晶體(M2)之背閘極(Back gate)與該第三 NMOS 電晶體(M3)之背閘極;以及一第 二控制節點(B2),係由該第三反相器之輸出端所形成,且連接至該第一 NMOS 電晶體 (M1)之背閘極:其中,該第一反相器和該第二反相器係呈交互耦合連接,亦即該第一反 相器之輸出端(即儲存節點 A)係連接至該第二反相器之輸入端,而該第二反相器之輸出 端(即反相儲存節點 B)則連接至該第一反相器之輸入端;而每一控制電路(2)更包含:一 第四 NMOS 電晶體(M21)、一第五 NMOS 電晶體(M22)、一第六 NMOS 電晶體(M23)、 一第七 NMOS 電晶體(M24)、一第八 NMOS 電晶體(M25)、一第九 NMOS 電晶體 (M26)、一第十 NMOS 電晶體(M27)、一第十一 NMOS 電晶體(M28)、一第十二 NMOS 電晶體(M29)、一第三 PMOS 電晶體(P21)、一第四 PMOS 電晶體(P22)、一第五反相器 (I21)、一延遲電路(Delay)以及一寫入控制信號(CTL)所組成;其中,該第四 NMOS 電晶 體(M21)之源極係連接至該第七 NMOS 電晶體(M24)之汲極,而閘極與汲極連接在一起並 連接至該第一低電壓節點(VL1);該第五 NMOS 電晶體(M22)之源極、閘極與汲極係分別 連接至接地電壓、一反相待機模式控制信號(/S)與該第二低電壓節點(VL2);該第六 NMOS 電晶體(M23)之源極、閘極與汲極係分別連接至該第二低電壓節點(VL2)、一待機模式控 制信號(S)與該第一低電壓節點(VL1);該第七 NMOS 電晶體(M24)之源極連接至接地電 壓,而閘極與汲極連接在一起並連接至該第四 NMOS 電晶體(M21)之源極;該第八 NMOS 電晶體(M25)之源極、閘極與汲極係分別連接至該第一低電壓節點(VL1)、該反相待機模 式控制信號(/S)與該第九 NMOS 電晶體(M26)之汲極;該第九 NMOS 電晶體(M26)之源極 係連接至接地電壓,而閘極與汲極連接在一起並連接至該第八 NMOS 電晶體(M25)之汲 極;該第十NMOS 電晶體(M27)之源極、閘極與汲極係分別連接至接地電壓、該第十一 NMOS 電晶體(M28)之汲極與該第九 NMOS 電晶體(M26)之閘極;該第十一 NMOS 電晶 體(M28)之源極、閘極與汲極係分別連接至該第十二 NMOS 電晶體(M29)之汲極、該寫入 控制信號(CTL)與該第十 NMOS 電晶體(M27)之閘極、該第三 PMOS 電晶體(P21)之汲極 和該第四 PMOS 電晶體(P22)之汲極;該第十二 NMOS 電晶體(M29)之源極、閘極與汲極 係分別連接至接地電壓、該第五反相器(I21)之輸出端與該第十一 NMOS 電晶體(M28)之 源極;該第五反相器(I21)之輸入連接至該延遲電路(Delay)之輸出,而該第五反相器(I21) 之輸出則連接至該第十二 NMOS 電晶體(M29)之閘極;該延遲電路(Delay)之輸入連接至 該寫入控制信號(CTL)與該第三 PMOS 電晶體(P21)之閘極和該第十一 NMOS 電晶體(M28) 之閘極;該第三 PMOS 電晶體(P21)之源極、閘極與汲極係分別連接至一電源供應電壓 (V<sub>DD</sub>)、該寫入控制信號(CTL)、與該第四 PMOS 電晶體(P22)之汲極和該第十一 NMOS 電晶體(M28)之汲極;而該第四 PMOS 電晶體(P22)之源極、閘極與汲極係分別連接至該 電源供應電壓(VDD)、該第五反相器(I21)之輸出與與該第三 PMOS 電晶體(P21)之汲極和 該第十一 NMOS 電晶體(M28)之汲極;再者,該反相待機模式控制信號(/S)係由該待機模 式控制信號(S)經一反相器而獲得;而該寫入控制信號(CTL)為一寫入致能(Write Enable, 簡稱 WE)信號與對應之字元線(WL)信號的及閘(AND gate)運算結果,亦即僅於該寫入致 能(WE)信號與該對應之字元線(WL)信號均為邏輯高位準時,該寫入控制信號(CTL)方為 邏輯高位準。

- 2. 如申請專利範圍第 1 項所述之單埠 SRAM,其中,該第一反相器為一 CMOS(互補金氧半導體)反相器,該第二反相器亦為一 CMOS 反相器。

- 3. 如申請專利範圍第 1 項所述之單埠 SRAM,其中,該第三反相器為一 CMOS 反相器,該 第四反相器亦為一 CMOS 反相器。

#### 圖式簡單說明

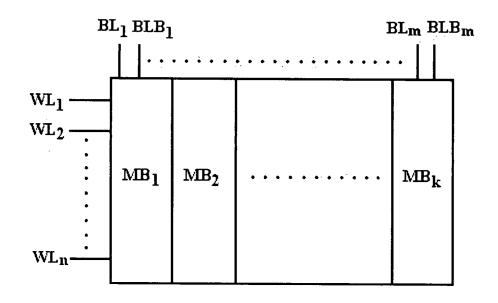

- 第 1a 圖 係顯示習知之靜態隨機存取記憶體;

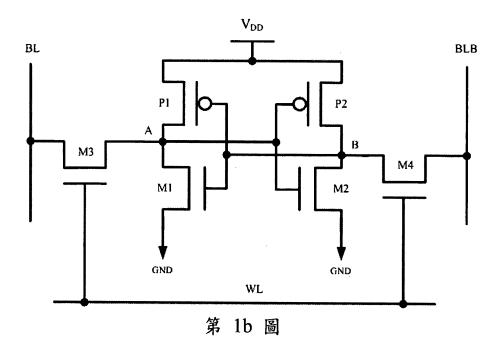

- 第 1b 圖 係顯示習知 6T 靜態隨機存取記憶體晶胞之電路示意圖;

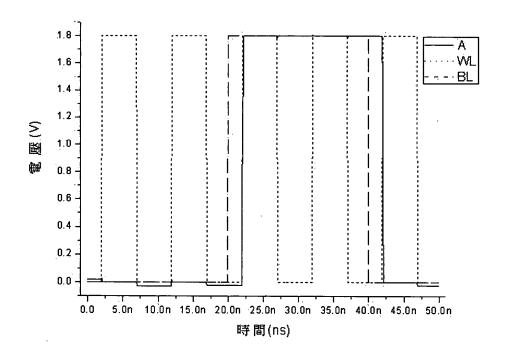

- 第2圖 係顯示習知6T靜態隨機存取記憶體晶胞之寫入動作時序圖;

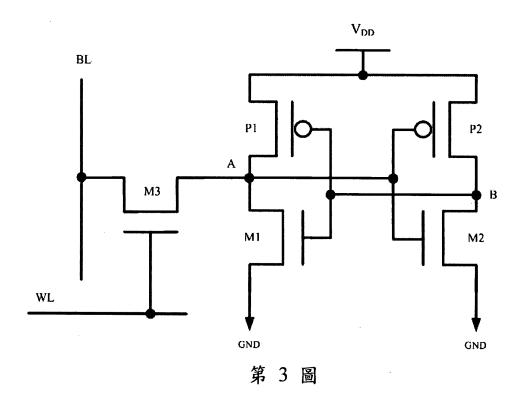

- 第3圖 係顯示習知5T靜態隨機存取記憶體晶胞之電路示意圖;

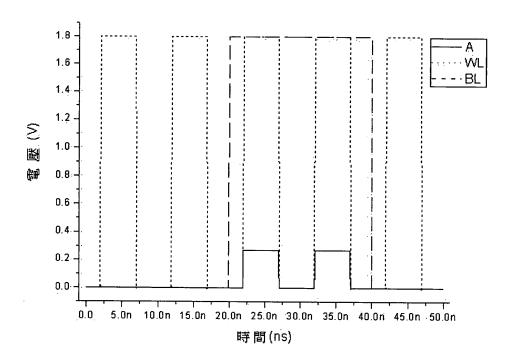

- 第 4 圖 係顯示習知 5T 靜態隨機存取記憶體晶胞之寫入動作時序圖;

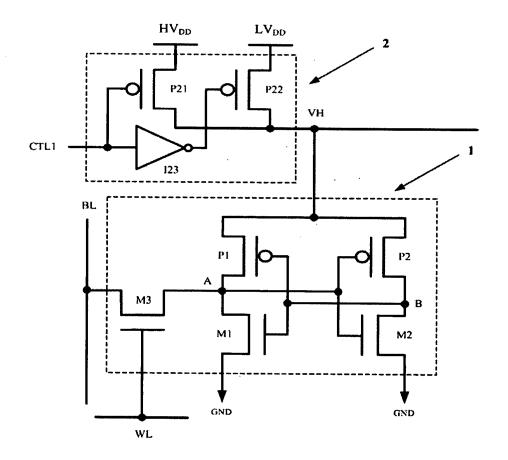

- 第5圖 係顯示習知第TW M358390號之5T 靜態隨機存取記憶體晶胞之電路示意圖;

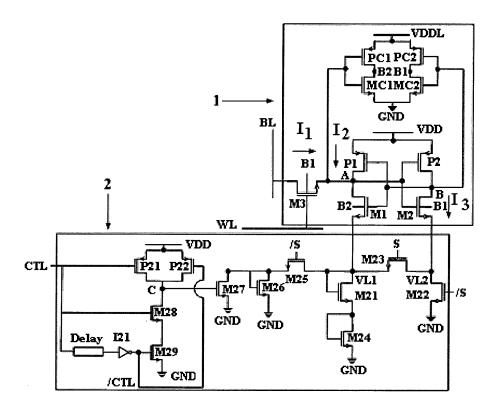

- 第6圖 係顯示本創作較佳實施例所提出之電路示意圖;

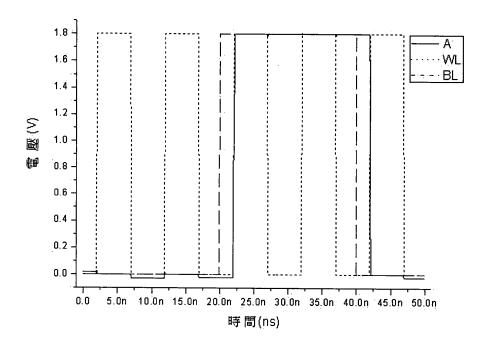

- 第7圖 係顯示第6圖之本創作較佳實施例之寫入動作時序圖。

# 第 1a 圖

# 第 2 圖

(5)

第 4 圖

第 5 圖

(6)

第 6 圖

第 7 圖