# 新型專利說明書

# 一、新型名稱:

電壓變換緩衝電路 Voltage Converting Buffer Circuit

# 二、中文新型摘要:

本創作提出一種新穎架構之電壓變換緩衝電路,其包括一 CMOS反相器1、一位準移動正反器2以及一N通道MOS電晶體 M10,其中該CMOS反相器1係由P通道MOS電晶體M1以及N通道 MOS電晶體M2所組成,並連接在第一電源電壓VCC1與接地之 間,該位準移動正反器2係由P通道MOS電晶體M3與M5以及N通 道MOS電晶體M4與M6所組成,並連接在第二電源電壓VCC2與 接地之間,而該N通道MOS電晶體M10係連接在第二電源電壓 VCC2與輸出端VOUT之間,且其閘極用以接收著由該CMOS反相 器1所輸出之反相的輸入電壓信號。由於本創作於輸出電壓 信號上升期間,輸入端VIN之輸入電壓信號僅需經由N通道 MOS電晶體M2之延遲,即可使N通道MOS電晶體M10導通,因 此,不但可較先前技藝具有更短之上升時間,並且因為不需 使用到延遲電路,因而也可有效簡化電路結構;此外,N通 道MOS電晶體M10亦可視情況調整其通道寬度(Channel width)W和零偏壓臨限電壓(Zero-bias threshold voltage) Vto之值,以改變或增加其驅動能力。

# 三、英文新型摘要:

# 四、指定代表圖:

- (一)本案指定代表圖為: 第四圖

- (二)本代表圖之元件符號簡單說明:

1···CMOS反相器

2・・・位準移動正反器

VIN···輸入端

VOUT··・輸出端

VCC1···第一電源電壓

VCC2···第二電源電壓

M1···第一PMOS電晶體

M2···第一NMOS電晶體

M3···第二PMOS電晶體

M4···第二NMOS電晶體

M5···第三PMOS電晶體

M6··・第三NMOS電晶體

M10···NMOS電晶體

### 五、新型說明:

#### 【新型所屬之技術領域】

[n] 本創作係有關於一種電壓轉換緩衝電路,尤指利用一CMOS 反相器、一位準移動正反器以及一N通道MOS電晶體所組成的電壓轉換緩衝電路。

#### 【先前技術】

- [n] 電壓變換緩衝電路係一種電子電路,其用以接收一輸入電壓信號,並將其電壓位準變換至另一較高電壓位準或另一較低電壓位準後輸出,以便適用於不同之裝置及/或系統之電源需求,例如,於中央處理單元(CPU)和記憶體之間就需要用到電壓變換緩衝電路。

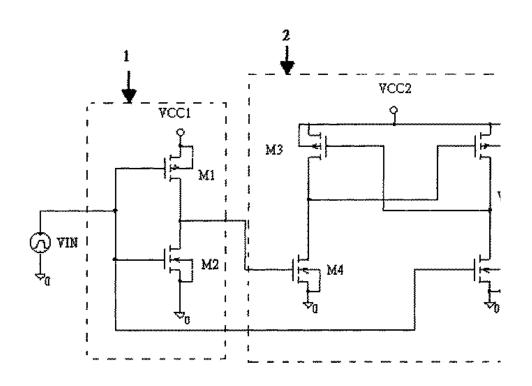

- [n] 在許多應用中,輸入電壓信號需要被反相,並將之改變至 另一適合的電壓位準以便適用於另一不同之裝置及/或系 統,例如,第一圖所示之習知電壓變換緩衝電路,即是一 例。第一圖所示之電壓變換緩衝電路係令一CMOS反相器1接 收一輸入電壓信號,並且輸出一被反相的電壓信號到一位準 移動正反器2,用以移動此經反相之輸入電壓信號之電壓位 準。

- [n] 請參考第一圖所示之電壓變換緩衝電路,當輸入端VIN為低邏輯位準時,P通道MOS電晶體M1導通(ON),而N通道MOS電晶體M2截止(OFF),這使得CMOS反相器1之輸出維持在高邏輯位準狀態。所以N通道MOS電晶體M4與M6分別為ON與OFF,因此,輸出端VOUT為一高邏輯位準(即 VCC2)。

- [n] 而當輸入端VIN為高邏輯位準時,P通道MOS電晶體M1截止 (OFF),而N通道MOS電晶體M2導通(ON),這使得CMOS反相器1 之輸出維持在低邏輯位準狀態。所以N通道MOS電晶體M4與M6分別為OFF與ON,因此,輸出端VOUT為一低邏輯位準(即零伏特)。

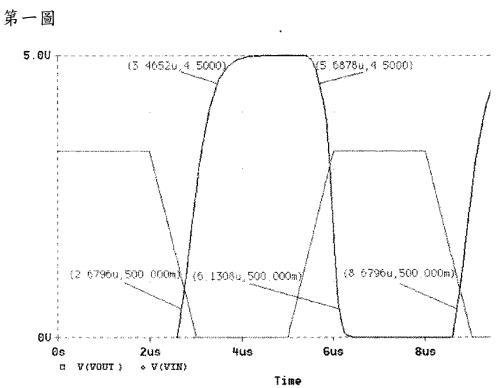

- [n] 第一圖之電壓變換緩衝電路之OrCAD Pspice暫態分析模擬 結果,如第二圖所示,其上升時間Tr(Rise time)為 0.7856us,而下降時間Tf(Fall time)為0.4430us,很明顯 地,上升時間遠比下降時間還要長。

- [n] 上升時間遠比下降時間來得長的原因如下:當輸入電壓信

號VIN由高邏輯位準變為低邏輯位準時,CMOS反相器1的輸出也由低邏輯位準轉變為高邏輯位準,但由於VCC1(3.3伏特)的電壓位準不夠高,所以CMOS反相器1在提供高邏輯位準給位準移動正反器2時的驅動能力較低(因位準移動正反器2係使用5.0伏特之電源電壓VCC2),因此,在位準移動正反器2中正反器需要一較長的時間才能使得N通道MOS電晶體M4之汲極電壓下降至足以使P通道電晶體M5導通(ON),於是,連帶使得P通道電晶體M5由截止(OFF)狀態轉變為導通(ON)的時間延長,結果,輸出電壓信號VOUT由低邏輯位準轉變為高邏輯位準的上升時間拉長。

- [n] 而當輸入電壓信號VIN由低邏輯位準轉變為高邏輯位準時,VCC1的電壓位準不夠高雖會使得N通道MOS電晶體M6之汲極電壓下降至足以使P通道電晶體M3導通(ON)的時間拉長,但由於該N通道MOS電晶體M6之閘極係直接連接至輸入電壓信號VIN,而非如上述之輸出電壓信號上升期間般,需經一CMOS反相器1反相、延遲方輸入至N通道MOS電晶體M4之閘極,並俟N通道MOS電晶體M4之閘極,並俟N通道MOS電晶體M4之股極電壓下降至足以使P通道電晶體M5導通(ON)後,才可使輸出電壓信號由由低邏輯位準轉變為高邏輯位準,與輸出電壓信號上升期間相比較,輸出電壓信號下降期間所經過的電晶體數較少,所以,下降時間會小於上升時間。

- [n] 對於許多應用而言,上述之上升時間高於下降時間係不欲 見到的,由於輸出電壓信號VOUT由低邏輯位準轉變為高邏輯 位準的上升時間拉長,在高速操作的環境下,將使得電壓變 換緩衝電路動作本身無法發揮其作用。

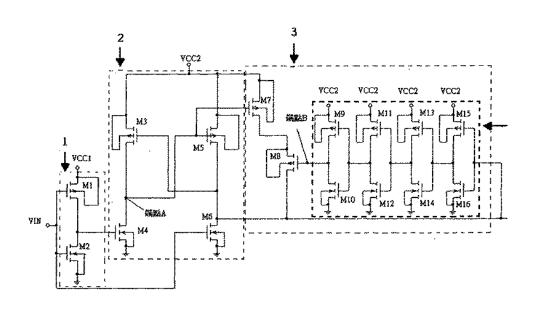

- 為了解決上述問題,另一先前技藝(即中華民國專利申請  $\lceil n \rceil$ 案號第87121232號專利案)被提出,其係由一CMOS反相器1、 一位準移動正反器2以及一延遲驅動器3所組成,如第三圖所 示。其中,當輸入端VIN為高邏輯位準時,P通道MOS電晶體 M1截止(OFF)且N通道MOS電晶體M2導通(ON),使得CMOS反相 器1之輸出維持在一低邏輯位準。所以N通道MOS電晶體M4與 M6分別為OFF與ON,而P通道MOS電晶體M3與M5分別為ON與 OFF, 至於新增之P通道MOS電晶體M7與M8則分別處於OFF與ON 之狀態,因此,輸出電壓信號VOUT為一低邏輯位準(亦即零 伏特)。當輸入端VIN為低邏輯位準時,P通道MOS電晶體M1導 通(ON)且N通道MOS電晶體M2截止(OFF),使得CMOS反相器1之 輸出維持在一高邏輯位準。所以,N通道MOS電晶體M4與M6分 別為ON與OFF,而P通道MOS電晶體M3與M5分別為OFF與ON,至 於新增之P通道MOS電晶體M7與M8則分別處於ON與OFF之狀 態,因此,輸出端VOUT為一高邏輯位準(亦即VCC2)。

反相,並將反相的資料信號藉由位準移動正反器2而移動至 另一電壓位準後,輸出於輸出端VOUT(其電壓擺幅被移動至 例如5.0伏特之VCC2與零伏特之間)。

- [n] 請再參考第三圖,當輸入端VIN之一輸入電壓信號由高邏輯位準變為低邏輯位準時,P通道MOS電晶體M1為ON,且N通道MOS電晶體M2與M6均為OFF。所以,P通道MOS電晶體M1將N通道MOS電晶體M4之閘極拉升至高邏輯位準,以開啟N通道MOS電晶體M4,接著並開啟P通道MOS電晶體M5與M7。此時,因所有的P通道MOS電晶體M5、M7、M8同時為ON,所以,結合來自P通道MOS電晶體M5之驅動電流以及來自P通道MOS電晶體M7與M8之驅動電流會將輸出端VOUT較快速地拉升至高邏輯位準。然後,輸出端VOUT之高邏輯位準的輸出電壓信號經由延遲區塊4傳送後,關閉P通道MOS電晶體M8。所以,輸出端VOUT可根據在輸入端VIN由低邏輯位準變化至高邏輯位準的轉變信號,將輸出電壓信號較快速地從低邏輯位準提升至高邏輯位準。

- [n] 雖說第三圖之先前技藝,於輸出電壓信號上升期間,可較快速地將輸出端VOUT之輸出電壓信號由低邏輯位準轉換為高邏輯位準,但其結構複雜(使用了延遲區塊4以及兩個新增之P通道MOS電晶體M7及M8),並且因為輸入端VIN之信號需經由N通道MOS電晶體M2及M4之延遲後,才能使新增之P通道MOS電晶體M7導通,因此,在縮短上升時間方面仍有改良空間存在。

- [n] 有鑑於此,本創作之主要目的係提出一種新穎架構之電壓 變換緩衝電路,其不但能進一步縮短上升時間,並且兼具電 路結構簡單、佔用的晶片面積小等多重功效。

- [n] 本創作之次要目的係提出一種不需使用到延遲電路之新穎 架構之電壓變換緩衝電路。

#### 【發明內容】

[n] 本創作提出一種新穎架構之電壓變換緩衝電路,其包括一CMOS反相器1、一位準移動正反器2以及一N通道MOS電晶體M10,其中該CMOS反相器1係由P通道MOS電晶體M1以及N通道MOS電晶體M2所組成,並連接在第一電源電壓VCC1與接地之間,該位準移動正反器2係由P通道MOS電晶體M3與M5以及N通道MOS電晶體M4與M6所組成,並連接在第二電源電壓VCC2與接地之間,而該N通道MS電晶體M10係連接在第二電源電壓VCC2與接地之間,而該N通道MS電晶體M10係連接在第二電源電壓VCC2與接地之間,且其閘極用以接收著由該CMOS反相器1所輸出之反相的輸入電壓信號。由於本創作於輸出電壓信號上升期間,輸入端VIN之輸入電壓信號僅需經由N通道MOS電晶體M2之延遲,即可使N通道MOS電晶體M10導通,因此,不但可較先前技藝具有更短之上升時間,並且因為不需使用到延遲電路,因而也可有效簡化電路結構;此外,N通

道MOS電晶體M10亦可視情況調整其通道寬度(Channel width)W和零偏壓臨限電壓(Zero-bias threshold voltage) Vto之值,以改變或增加其驅動能力。

#### 【實施方式】

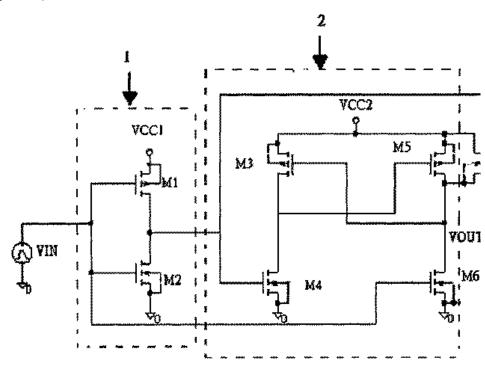

- [n] 根據上述之目的,本創作提出一種電壓變換緩衝電路,如第四圖所示,其係由一CMOS反相器1、一位準移動器正反器2以及一N通道MOS電晶體M10所組成。該CMOS反相器1係由一第一PMOS電晶體M1以及一第一NMOS電晶體M2所組成,其中,該第一PMOS電晶體M1之源極連接至第一電源電壓VCC1,閘極連接至輸入端VIN,而汲極則與第一NMOS電晶體M2之汲極相連接;而該第一NMOS電晶體M2之源極接地,閘極連接至輸入端VIN,而汲極則與第一PMOS電晶體M1之汲極相連接。

- [n] 該位準移動正反器2係由第二PMOS電晶體M3、第二NMOS電晶體M4、第三PMOS電晶體M5以及第三NMOS電晶體M6所組成,其中,該第二PMOS電晶體M3之源極連接至第二電源電壓VCC2,間極與第三NMOS電晶體M6之汲極相連接,並連接到輸出端VOUT,汲極與第二NMOS電晶體M4之汲極相連接並連接到第三PMOS電晶體M5之間極;該第二NMOS電晶體M4之源極接地,間極連接到該CMOS反相器1之輸出端,而汲極則與第二PMOS電晶體M3之汲極相接並連接到第三PMOS電晶體M5之間極;該第三PMOS電晶體M5之源極連接至第二電源電壓VCC2,間極與第二NMOS電晶體M5之源極裡接至第二門MOS電晶體M3之汲極相連接,並連接到輸出端VOUT;而該第三NMOS電晶體M6之源極接地,間極接到輸出端VOUT;而該第三NMOS電晶體M6之源極接地,間極接到輸出端VOUT。

- [n] 請參考第四圖,本創作於第二電源電壓VCC2與輸出端VOUT之間增設有一N通道MOS電晶體M10,且其閘極用以接收由該CMOS反相器1所輸出之反相的輸入電壓信號,因此,於輸出電壓信號上升期間,輸入端VIN之輸入電壓信號僅需經由N通道MOS電晶體M2之延遲,即可先令N通道MOS電晶體M10導通,並對輸出端VOUT充電。結果,可較先前技藝具有更短之上升時間,並且可視情況調整該N通道MOS電晶體M10之通道寬度(Channel width)W和零偏壓臨限電壓(Zero-bias threshold voltage)Vto之值,以改變或增加其驅動能力,進而改變或進一步縮短上升時間。

- [n] 請再參考第四圖,當輸入端VIN為高邏輯位準時,第一PMOS 電晶體M1截止(OFF),而第一NMOS電晶體M2導通(ON),使得 CMOS反相器1之輸出維持在低邏輯位準狀態,所以第二與第 三N通道MOS電晶體M4與M6分別為OFF與ON,而第二與第三P通道MOS電晶體M3與M5分別為ON與OFF,至於新增設之N通道MOS 電晶體M10則處於OFF狀態,因此,輸出端VOUT為邏輯低位準

(即零伏特)。

- [n] 當輸入端VIN為低邏輯位準時,第一PMOS電晶體M1導通 (ON),而第一NMOS電晶體M2截止(OFF),使得CMOS反相器1之輸出維持在高邏輯位準狀態,所以第二與第三N通道MOS電晶體M3與M5分別為ON與OFF,而第二與第三P通道MOS電晶體M3與M5分別為OFF與ON,至於新增設之N通道MOS電晶體M10則仍處於OFF狀態(該新增設之N通道MOS電晶體M10於CMOS反相器1之輸出上升至該N通道MOS電晶體M10之臨限電壓(Threshold voltage)時開始導通,而於輸出端VOUT之電壓上升至第二電源電壓VCC2扣抵一該N通道MOS電晶體M10之臨限電壓後截止),因此,輸出端VOUT為一高邏輯位準(亦即第二電源電壓 VCC2)。

- 而當輸入端VIN由高邏輯位準轉變為低邏輯位準時,第一  $\lceil n \rceil$ PMOS電晶體M1為導通(ON),第一NMOS電晶體M2為截止 (OFF),使得CMOS反相器1之輸出由低邏輯位準狀態轉變為高 邏輯位準狀態,當該CMOS反相器1之輸出上升至N通道MOS電 晶體M10之臨限電壓時,該N通道MOS電晶體M10開始導通,於 是可提早對輸出端VOUT進行充電動作,此時由於第二NMOS電 晶體M4亦為導通(ON),因而可將該第二NMOS電晶體M4之汲極 電壓往下拉,俟該第二NMOS電晶體M4之汲極電壓下拉至第二 電源電壓VCC2扣抵一第三P通道MOS電晶體M5之臨限電壓的絕 對值時,該第三P通道MOS電晶體M5開始導通,於是可藉雙電 流路徑(一為來自N通道MOS電晶體M10之電流路徑,另一為來 自第三P通道MOS電晶體M5之電流路徑),快速拉升輸出端 VOUT之電壓,當輸出端VOUT之電壓快速上升至第二電源電壓 VCC2扣抵一該N通道MOS電晶體M10之臨限電壓後,該N通道 MOS電晶體M10隨即截止,此時,僅剩下來自第三P通道MOS電 晶體M5之電流路徑,將輸出端VOUT之電壓上拉至第二電源電 壓VCC2。

- [n] 由上述之分析可知,於輸出端VOUT之輸出電壓信號上升期間,輸入端VIN之輸入電壓信號僅需經由第一N通道MOS電晶體M2之延遲,即可使增設之N通道MOS電晶體M10導通,並且可藉雙電流路徑(一為來自N通道MOS電晶體M10之電流路徑,另一為來自第三P通道MOS電晶體M5之電流路徑),來快速拉升輸出端VOUT之電壓,因此,可較先前技藝具有更短之上升時間,並且因為輸出電壓信號上升至第二電源電壓VCC2扣抵一該N通道MOS電晶體M10之臨限電壓後,即自動關閉該N通道MOS電晶體M10,因而並不需設置延遲電路,所以亦可有效簡化電路結構。此外,N通道MOS電晶體M10亦可視情況調整其通道寬度(Channel width)W和零偏壓臨限電壓(Zero-bias threshold voltage)Vto之值,以改變或增加其驅動能力,進而改變或進一步縮短該上升時間。

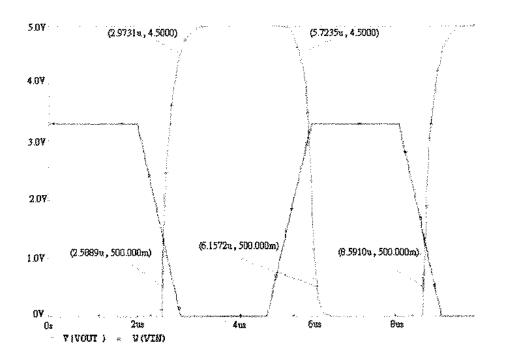

[n]本創作所提出之電壓變換緩衝電路之OrCAD PSpice暫態分模 擬結果如第五圖所示。第五圖係以level 3模型並使用0.35 微米CMOS製程參數加以模擬(其PMOS電晶體和NMOS電晶體之 零偏壓臨限電壓 $V_{TO}$ 分別為-1V和1V),且電源供應電壓VCC1等於3.3伏特、VCC2等於5伏特,PMOS電晶體M1、M3、M5之通 道寬長比均為(2\*0.35μm/0.35μm), NMOS電晶體M2、M4、M6 之通道寬長比為(0.35μm/0.35μm), 而NMOS電晶體M10之通 道寬長比為(24\*0.35μm/0.35μm)、N通道MOS電晶體M10之零 偏壓臨限電壓V<sub>TO</sub>為0.65伏特。由第五圖之結果可知,本創 作之上升時間Tr(Rise time)為0.384us,而下降時間Tf (Fall time)為0.433us,很明顯地,可有效解決先前技藝上 升時間不夠快之問題。此外,亦可視情況調整N通道MOS電晶 體M10之通道寬度(Channel width)W和零偏壓臨限電壓 (Zero-bias threshold voltage)Vto之值,以使上升時間Tr 等於下降時間Tf。

#### 【圖式簡單說明】

- [n] 第一圖係顯示先前技藝一之電壓變換緩衝電路圖。

- [n] 第二圖係顯示第一圖電壓變換緩衝電路之輸入電壓信號及輸出電壓信號之暫態分析時序圖。

- [n] 第三圖係顯示先前技藝二之電壓變換緩衝電路圖。

- [n] 第四圖係顯示本創作之電壓變換緩衝電路圖。

- [n] 第五圖係顯示第四圖電壓變換緩衝電路之輸入電壓信號及輸出電壓信號之暫態分析時序圖。

### 【主要元件符號說明】

- [y] 1···CMOS反相器

- [v] 2···位準移動正反器

- 「v 3・・・延遲驅動器

- [y] 4···延遲區塊

- 「v VIN···輸入端

- [y] VOUT···輸出端

- 「v VCC1···第一電源電壓

- [y] VCC2···第二電源電壓

- 「v M1···第一PMOS電晶體

- 「y M2・・・第一NMOS電晶體

- [y] M3··・第二PMOS電晶體

- 「y M4···第二NMOS電晶體

- [y] M5··・第三PMOS電晶體

- [y] M6··・第三NMOS電晶體

- 「y M7・・・P通道MOS電晶體

- [v] M8···P通道MOS電晶體M8

- 「v] M10・・・NMOS電晶體

# 六、申請專利範圍:

1.一種電壓變換緩衝電路,用以反相並改變一電壓信號所需要之邏輯位準,其包括:一輸入端(VIN),用以提供一輸入電壓信號;一輸出端(VOUT),用以輸出反相並改變後的電壓信號;一第一電源供應電壓,用以提供CMOS反相器(1)所需之第一電源電壓(VCC1);一第二電源供應電壓,用以提供位準移動正反器(2)所需之第二電源電壓(VCC2);一CMOS反相器(1),用以將輸入電壓信號予以反相處理,並輸出一反相的輸入電壓信號;一位準移動正反器(2),用以移動該反相的輸入電壓信號之電壓位準至另一不同之電壓位準;以及一N通道MOS電晶體(M10),該N通道MOS電晶體(M10)係連接在第二電源電壓(VCC2)與輸出端(VOUT)之間,且其閘極用以接收該反相的輸入電壓信號。

2. 如申請專利範圍第1項所述之電壓變換緩衝電路,其中該CMOS反相器(1)更包括:一第一PMOS電晶體(M1),其源極連接至第一電源電壓(VCC1),閘極連接至輸入端(VIN),而汲極則與第一NMOS電晶體(M2)之汲極相互連接;以及一第一NMOS電晶體(M2),其源極接地,閘極連接至輸入端(VIN),而汲極則與第一PMOS電晶體(M1)之汲極相互連接。

3.如申請專利範圍第1項所述之電壓變換緩衝電路,其中該位準移動正反器(2)更包括:一第二PMOS電晶體(M3),其源極連接至第二電源電壓(VCC2),閘極與第三NMOS電晶體(M6)之汲極相連接,並連接到輸出端(VOUT),汲極與第二NMOS電晶體(M4)之汲極相連接並連接到第三PMOS電晶體(M5)之閘極;一第二NMOS電晶體(M4),其源極接地,閘極連接到該CMOS反相器(1)之輸出端,而汲極則與第二PMOS電晶體(M3)之汲極相接並連接到第三PMOS電晶體(M5)之閘極;一第三PMOS電晶體(M5),其源極連接至第二電源電壓(VCC2),閘極與第二NMOS電晶體(M4)之汲極相連接並連接第二PMOS電晶體(M3)之汲極,而汲極則與第三NMOS電晶體(M6)之汲極相連接,並連接到輸出端(VOUT);以及一第三NMOS電晶體(M6),其源極接地,閘極接到輸入端(VIN),汲極與第三PMOS電晶體(M5)之汲極相接並連接至輸出端(VOUT)。

## 七、圖式:

第二圖

第二圖

第三圖

第三圖

第四圖

第四圖

第五圖

第五圖